# rp8601

a complete applicative processing concept

by

Gunnar Carlstedt, Carlstedt Elektronik AB

### Abstract:

An applicative real-time multiprocessor is described. Machine language, communication and integrated circuit implementation are applicative and based on graph rewriting.

User processes are applicative and is a derivation from HDLs. The machine language is a full-fledged applicative language with influences from functional and logic languages.

High order functions are complemented by a more general concept where programs are representations described in the basic language. It is an extension of a quoting mechanism.

Times for ports are synchronized. Input and output are timed. A real-time system performs a unification between a set of courses of events and the port values. Binding strength defines the port direction.

The machine is based on graph reduction described by equivalence rules. The control of a multiprocessor is by emitting such rules and implementing a structure arithmetic unit rewriting a two level expression. Garbage collection is a real time execution in parallel with the problem domain.

The multiprocessor consists of a rich network and a massive number of reduction processors. They store expressions as words as well in communication ports, clock, arithmetic unit as memory. The memory is associative.

### **Keywords:**

allocation, alternative, applicative process, applicative, behavior, data-path, equivalence rule, garbage collection, graph rewriting, H language, identifier domain, integrated circuit, interpretation, massive parallelism, memory, multiprocessor, processor, real-time, representation, scheduling, unification

### Licenses

This work is licensed under the Creative Commons Attribution-NonCommercial-NoDerivs 3.0 Unported License. To view a copy of this license, visit

http://creativecommons.org/licenses/by-nc-nd/3.0/ or send a letter to Creative Commons, 444 Castro Street, Suite 900, Mountain View, California, 94041, USA.

# INTRODUCTION

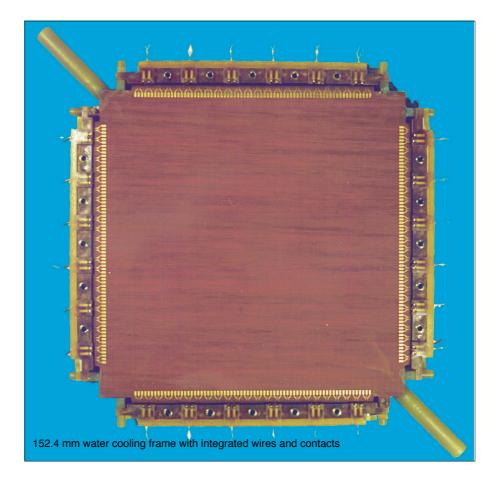

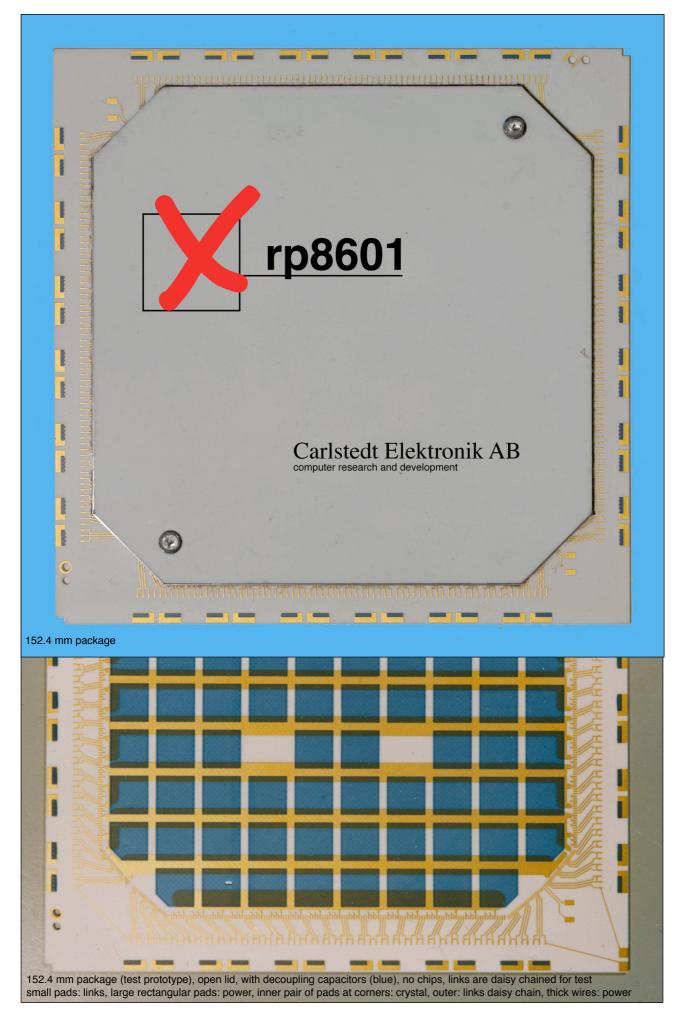

I performed from the early 1970's a number of multiprocessor architecture projects. With the experience together with funding from Swedish air-force a project aiming at a new design concept was formed. The project was named **rp8601** (=reduction processor, year 1986, number 1). Further on ASEA (now ABB Ltd) took over the project. ASEA was split into ABB Ltd and Incentive AB, who made a considerable investment in the project. The project was shut down 1994 due to other interests of the mother company.

This report describes the rp8601 architecture. During this large project a number of changes were made due to requests by the funder. However the report describes the original ideas together with the experience from the project.

The concept WYSWYG (What You See What You Get) for document editors was introduced during the 1980's. The change was dramatic compared to earlier methods. Young people of today would think of the earlier methods as awkward, slow, farfetched and error prone.

Early computer languages like FORTRAN developed to more rich languages. The size of the languages exploded, with Algol 68 as an extreme. Subsets as Jovial, Pascal and Modula was much less in size. Unix came with C. The development was by software system engineers. Meanwhile a mathematically based community introduced languages based on *lambda calculus*. Lisp was followed by a number of functional languages like ML and further on by Haskell. Meantime a new paradigm, the *logic language* based on *Horn clauses*, was created with Prolog as its first language. These late languages are applicative and would be the computer language counterpart to WYSWYG.

None of these languages could directly model hardware, time and processes. Simula 67 introduced a concept of message passing. Later on more mathematically based initiatives created *process algebras* such as CSP and CCS. Message passing could be viewed as a side effect. Even if they use a functional approach when describing creating and receiving the messages the system described would not be side-effect free.

Other system maintenance and control is not supported by the languages. Instead other types of maintenance concepts are shoe horned into the software.

Meanwhile the silicon circuit community designed their abstractions. They described hardware. In contrary to the software approaches everything was in parallel. Spice was an early language where everything was components and analogue signals. Later VHDL was introduced - a committee work, probably with people from different communities. It worked in two modes - the *procedural* and the *applicative*! Hardware description languages, HDL, introduced the concept of component, parameterised components, libraries and communication between components. They also introduced wave forms - a way to describe the output/input for a process.

The applicative languages has now been present for about 30 years and still they are not popular. The community is rather small and in the development was more to be expected. However organizations using the concept have good experience. The HDLs are a must in the industry. At the time rp8601 started there was hardly no industrial projects using applicative languages and the experience was low.

The wish list from system designers was long. The rp8601 was a challenge to replace the von Neumann computer architecture by an applicative approach. Much was to be developed. Were there any key issues that has to be solved in order to facilitate a complete applicative computer system?

# **PROBLEMS - CHALLENGES**

Traditional von Neumann computers have influenced the thinking in computing in such a high way that it is hard to step outside this paradigm. This is the case from high level architecture and down to gates. The rp8601 is an attempt to step outside that paradigm. This will influence almost everything from languages over architecture down to gates. In this section a birds view is used to point out challenges to solve.

### Massive multiprocessing

rp8601 approach is a scalable architecture from small and simple to large massive parallel approaches. Traditional high performance computers consists of rather few traditional processors with some type of communication devices. Applications are allocated to processors and memory cells. The rp8601 goal is to have a space of molecules being processors. Within this structure the representation of an application is floating. There is some type of communication between the molecules. From performance point of view this allows the highest possible allocation of executing resources. From flexibility point of view the structure could be squeezed to fit an application.

The idea is that the problem should be loaded in the computer by almost neglecting its structure in a corresponding way that cash memories implements an invisible memory hierarchy.

In order to facilitate this, the problem loaded must be represented in such a way that it contains all information on synchronization, communication etc needed in a distributed environment. From my understanding the only available form is a directed graph. The vertices are tiny processes controlling itself and its directed edges. One of the possible execution mechanisms is graph reduction.

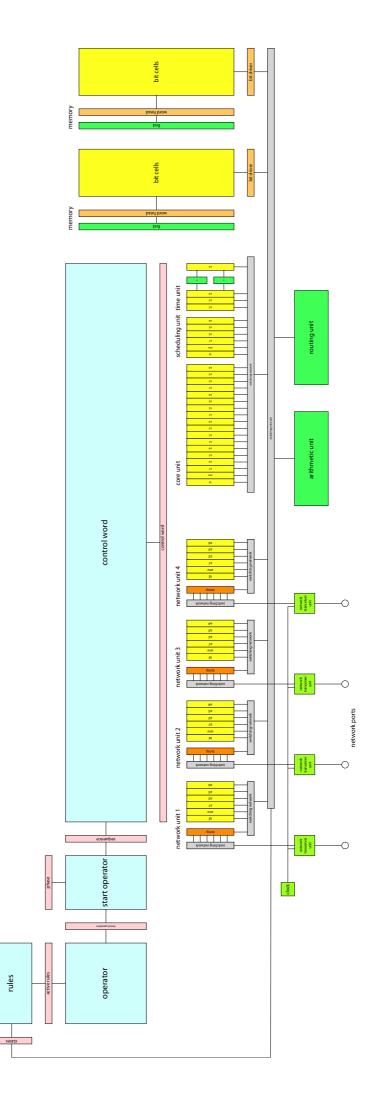

The rp8601 implements this by using a small process called closure. It stores an expression in the size of 4 words.

Key issues: performance, flexibility, scalability

### Trace graph - a tool

Traditionally, single processor application performance analysis is based on counting processor cycles. The hardware influence is almost only a weighted average between execution time of instructions. When cash memories are used the problem of "locality" or working set complicates the analysis.

When using a multiprocessor based on traditional processors with or without cash memories this analysis is not easy. Communicating processes form an execution order that is almost impossible to analyze. Only with a detailed knowledge of the application an estimate could be done.

The graph reduction situation is quite different. The graph is well specified. A method based on a "trace graph" is used. It contains all expressions used when executing the graph. It corresponds to an expansion of the graph to all its parts used during the execution.

An analysis of the trace graph gives:

- each edge in the graph uses one read, one write operation and one communication,

- each expression-rewrite corresponds to one vertex rewrite

- the trace graph has a depth being the length from the root to the leaves

the size is described by the number vertices and the number of edges

In a large problem the depth is generally much less than the size. The effective latency time is the longest of the vertices rewrites (including reads and writes) and communication over edges.

The time of a vertex rewrite is constant. The communication time is dependent on the "length" of the edge. For a given graph the number of vertex operations is fixed. There is a mean number of edges directed to a vertex. There is a ratio of link communication time to vertex rewrite time. These three numbers signify an execution of an application.

To improve performance vertices with many edges are to be duplicated and placed more local. Vertices are allocated in order to reduce the edge length.

The challenge is to use such a tool to analyze how to allocate and schedule a problem.

Key issues: performance analysis

### Address domains

Traditional multiprocessors may have a shared memory or a number of local memories. They use an address being number to depict a memory cell. Because the rp8601 consists of a structure of molecule processors such an address scheme is not possible.

All edges pointing to the same vertex are named a net in rp8601. The address is a mechanism to specify the nets. There are graph rewrite operations on nets. Therefore the mechanism of addressing is to be integrated with the rewrite operations.

The rp8601 implements the addressing by one domain for each net. A domain specifies a number of molecules. There is a constructor for a domain specifying its size and its placement in the molecule structure. An address is a number depicting a molecule and the domain constructor.

The constructor must be able to specify overlapping domains of the same size or any size in order not to place restrictions on the graph. Performance is dependent on the size and placement of a domain. It is heavily influenced by the communication structure.

The challenge is to design the domain constructor.

Key issues: addressing, synchronization, critical region, performance

### Partitioning

Traditional computers may have ports and processors implemented in separate subsystems. Special

purpose protocols are used to maintain a system structure and the intermodule communication. Traditionally, such communication may be: on low level I2C busses, device specific like SCSI, and system general as ethernet.

rp8601 uses a molecular approach. The application is an expression being loaded. The computer may be divided into a number of separate clusters each containing a number of molecules. With some mechanism parts of the expressions are allocated to clusters. By using the domain mechanism the the communication works.

In the long run this may be a method to integrate computers to ONE system. Communication is by expressions instead of awkward protocols. However high level intersystem communication protocol must still exists - they are the applications.

Some applications are rather stiff and controlled. Others are more lose where subsystems may be separated, i e lose communication. Such systems may be started again and reconnected.

rp8601 allows such disconnection, of course with a delay of pending expressions. However, there is a more fundamental issue to be solved: time. When systems are separated they loose time synchronization. Time elapses with different speed in the subsystems. When reconnected they have different time. It is not understood how to handle this.

Key issues: distributed computing, protocol, time, real systems

### Graph reduction

Graph reduction is straight forward to implement in a single processor. Using many processors complexity increases. The problem to solve is addressing, critical regions and synchronization.

rp8601 solves this by letting each vertex be a separate process. There are two rewrite operations: one for just the vertex and another for the net pointing to the vertex. The first one is simply like a traditional instruction. The challenge is to design the net rewrite.

rp8601 uses the H protocol in the domain of a net. The protocol publishes equivalence rules. They may be performed any time and several times.

Key issue: applicative, synchronization, critical region

### **Real time - behavior**

Traditional computers don't know about time. A special register giving a date may be used. Behavior is implemented by synchronization messages. In small single processors this may be sufficient, but for distributed and large machines problems arise. The arrival order of message may cause racing problems and in-determinant results.

The challenge is to make real-time first class. In order to do this the mechanism of a port and the basic (boot) execution mechanism has to be given a theoretical model. In the rp8601 case an applicative model. As I understand this has never been done before!

In order to be first class real-time behavior must fulfill a number of properties: storable, readable, referable, be operated, recorded and play backed. When recorded or play backed it may involve ports. Behavior may be either a structure of transactions or the corresponding with absolute or relative time stamps. Ports must be synchronized.

The rp8601 models a behavior by a data structure. As such all types of first class operations may be performed on it. Clock is a global feature. Absolute time occurs synchronized in all molecules. The port mechanism is a behavior simultaneously recording and performing play back.

Key issues: first class, port, synchronization, protocol, theoretical model

### Parallel modules, boot and I/O

In a traditional computer the boot mechanism is arbitrary. Starting a system with many or a vast amount of processors is feasible. However when starting at different time communication protocols have to perform a synchronized start. Using a vast amount of molecular processors a more delicate mechanism is needed.

The challenge is to understand what computing is in the regards of ports and internal execution.

rp8601 solves this in a very different way. First, modules are expressions (data structures) being fixed or behaviors. Modules communicate by unifying parts of such expressions . Ports are behaviors. Input/output is performed by unifying an internal behavior with the port behavior!

Booting is performed by emitting an expression into the computer. Several such expression may be emitted at any time. Thus booting may be performed for subsystems using different ports. A read-only memory may emit such a structure when started.

The mechanism is applicative.

Key issues: synchronization, port, booting, communication, applicative

### Executing memory

A traditional von Neumann computer like x86 (not rp8601) has a memory and a processor. Both are

separated, however a cash memory may be included in the processor package. The interface is a protocol performing read and write of memory locations. The processor has very little structure except for some registers. It could be considered a heap of gates.

The basis for rp8601 is a molecular approach. Of course, it is not feasible to have one physical processor in each memory cell, but memory cells may be multiplexed by a processor. This mimics a memory cell having a virtual processing capacity.

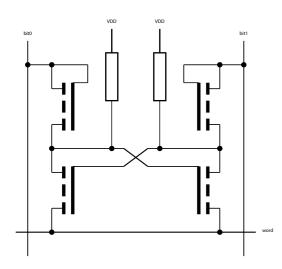

Graph reduction is generally not numerics. Instead it is based on pattern matching. As such a completely different electrical implementation could be used. It is based on transportation and associative comparisons in the memory, data-path and the control module. The challenge is to design such a processor.

The H processor implements one minute domain.

Key issues: processor, control, circuit

### Complete approach

In traditional computers there is an instruction set architecture. The architecture has no formal mathematical model. Thus any type of execution may be performed. This results in a flexibility. It can be used for any type of maintenance or implementation of tools etc. An example is a debugger.

Graph reduction implements an application being applicative. On the lowest level the implementation uses an "instruction"-level language. It could be a traditional instruction set architecture or an applicative language. If an applicative language is used there must be means to implement the mentioned maintenance and tools.

The challenge is to design an application machine level language fulfilling these requirements.

The rp8601 uses the H language being a single level approach.

Key issues: machine language, low level control

### Representation

I am watching a person performing the "real" steps of throwing a dice every 3rd second with the result 4, 6, and 2. On a paper I write " throwing a dice every 3rd second with the result 4, 6, and 2".

The first one is a real behavior and the second one a representation for this course of events. Instead of using plain text other more strict forms may be used.

Another example is "5+3". Written on a paper it is 3 tokens. Written in a computer language it represents the constant 8. But if I use an editor and want

to change it to "5+4", the text stands for 8, how do I proceed?

The new concept of "representation" is defined: there is the duality *item* and *representation* of item. By making a **derepr** of a representation an instance is created. Thus **derepr** "5+3" results in 5+3 and subsequently in 8. The **repr** goes the other way but is tricky, there are an infinite number of ways to express 8.

A simplified version of this is the Quote mechanism in Lisp. Modern languages don't have the concept. Functional languages use high-order functions to alter the semantics of a function, but this is not at all the same.

The introduction of *representation* gives a new understanding of symbols, function application, module instantiation, version handling etc. It also enables a mathematical understanding of execution, debugging and tracing.

Key issues:language, representation

### Behavior

Parallelism, the process concept and communication are all part of the same issue. The understanding of them is inherited from the sequential form of earlier languages. They are just other forms of doing assign (:=).

A new concept "*course of events*" (sv = händelseförlopp) is defined. Here are some examples:

- 1. a movie 51 minute long

- 2. throwing a a dice every 3rd second with the result 4, 6, and 2.

Both could be modeled. They can be stored, copied, and read. They can be performed any number of times. They could be analyzed, a part may be extracted, run stepwise, different speed, forward and backward. They are first class!

In the second case the outcome may be another course of events

3. throwing a a dice every 3rd second with the result 1, 4, and 3.

A new concept "*behavior*" is defined. It is a set of course of events. This set should be considered all course of events for a particular process. Thus "throwing a dice 3 times every 3rd second" has the outcome of  $6^3$  number of course of events. Another behavior would be when the delay between the throws is within the interval 0...10s.

The behavior concept described is a "natural one". A mathematical one used in computing consists of

other concepts also being behaviors. Thus a computational behavior is the cross product of

- ★ abstractions

- ★ symbols

- ★ modules

- ★ executions

- ★ resources

Each as to be explain further. Below the word "item" is used for what is described. An item may be a course of events or a behavior.

#### Abstraction

This is the top down method to construct. Generally it includes the use of modules for the decomposition, and basic symbols for depicting items. Symbols is used to form relations being equalities. In classical languages this is the intention of a function body. As such it may evolve by time, i e being a course of events!

### Symbols

This is a syntactic element. Hardware, global address, name, character etc are examples. They have an appearance but only depict a particular "knowledge". A more complicated one is the language used. As such it may evolve by time, i e being a course of events.

#### Modules

This a "component". Several such are fitted together. Generally parameters are used to define them. In almost all computer languages equality is used to fit them together, however implemented in different ways (argument, variable, element of message etc). The components may evolve, i e being a course of events.

#### Resources

This is the "physical" part of an implementation. The part is an item or generally a set of items. As such they could be physical parts as harbors, vessels etc as processors and memory cells.

#### Execution

This is the procedure to make an instance of an item using resources. As such it includes the binding of values to memory cells, ports and the rewrite process (order and allocation in time) to change the values of memory cells. Or as in the example above bind cargo to vessels and harbors.

Key issues: time, behavior, protocol

#### Indeterminism

I am using a calculator pressing 5 + 3 = and the response is 8 as it should. Then calculator continues to return 8 every time I repeat the sequence. Now assume that there is an error in the calculator. It returns arbitrary result each time. The first example is a *deterministic* and the second one a *nonde*- *terministic* behavior. This is the established mathematical understanding.

Assume now that we have a real time computer system. Two experiments are done with the same history. In both cases exactly the same input is used by the computer. A computer is an extremely large finite state machine. Thus it produces the same result in both cases. Now assuming that arbitrary but equal input is used. The results would be the same. The result is deterministic!

On the other hand, if we record the input to the system, even if the history is the same, generally the next input is variable, thus the input from *real world* is nondeterministic!

The input to the computer is read by a device with somewhat uncertainty (jittering) in time. Thus two identical input sequences may not produce the same result from the input device. The input is *nondeterministic*. The output from the computer may therefore be nondeterministic.

As a designer of a real time system I want the same result from the same input, i e deterministic.

The general opinion in the computer community is that real time systems are nondeterministic and should so be! The reason behind this is probably that the implementation is constructed by message passing! **My understanding is different**.

Using a large asynchronous multiprocessor using message passing technique may cause message arrival order to be nondeterministic. The system may therefore behave nondeterministically.

In order to produce deterministic results the message passing semantics have to be redesigned or replaced by other mechanisms.

Using a perfect method in a large system would cause the system to be stiff. Because of design flaws, machine errors, overload situations the output cannot be guaranteed. In such cases nondeterminism may be a design goal!

Key issues: process, communication

### **OVERVIEW**

A guided tour within the rp8601 is in this section. The explanations are sketchy and simplified in order to make the description more comprehensive.

### Process concept

Ports are for input and output. The port has an outside being the real world and an inside being a data structure. The general idea behind the rp8601 port is that the internal data structure should be a model of the real world behavior regardless of being an input or output port.

The internal data structure is a course of events. Beside an example is shown. It consists of a list tagged **seq** and a number of time stamps (t123.3 etc) separating the

values (56 etc) on the real world side.

### seq[t123.3 56 t127.2 23 t129.4]

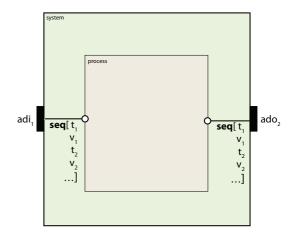

There is a system process (behavior) that is the boot mechanism, see figure below:

unify[ apply[ par[adi<sub>1</sub> ado<sub>2</sub>]] bootstrap]

The boot is a unification between the ports and the bootstrap. The ports are described by the symbols (hardware addresses  $adi_1$  and  $ado_2$  depicting the ports). The standard list in rp8601 is tagged **par**. Here the list is considered a representation for the ports.

The **apply**-construct transforms the representation into the port internal course of events.

unify[ par[in1 out2] bootstrap]

The unification between the boot strap and the port behavior causes the binding of the internal behavior of the bootstrap to the in- and outports.

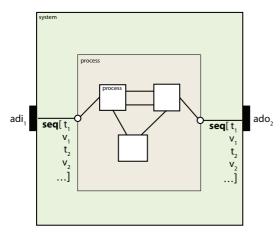

As an example the bootstrap process could further be divided into 3 processes (components) as shown below:

The lines (nets) are behaviors local to the bootstrap process. They are somewhat the same as variables in normal languages and nets in hardware description languages. Each of these nets are bound with unification to the local processes. The local components are <u>relations</u> between their behaviors connected to their interface.

All these behaviors (excluding the input output) are deterministic. The concept of unification, i e equality, makes the total structure deterministic.

In a unification of two expressions one could be bound to a value and the other not. The equality forces the unbound to the value of the bound one. Thus there is a flow of value from the bound to the unbound. This mechanism causes the flow of values from input towards the output and eventually to the output port data structure.

The bootstrap module concept is the same as the internal module concept, thus making the module concept orthogonal throughout the system.

### Generators

Generators are modules used to create predefined representation for behaviors. It is a module having a hidden internal structure and an external being its interface. Generators corresponds to parameterised components in hardware description languages and procedures in logic language. A distant relative in the process algebras are processes.

In this section some few toy like generators are used to show the concept. The earlier discussed bootstrap is described. Generally the behavior consists of two elements where the first is the input and the last the output.

#### Constant

Assume that the input port has one and only one course of events. The output port the corresponding. This is a toy behavior of no use:

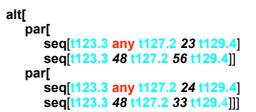

par[ seq[t123.3 56 t127.2 23 t129.4] seq[t123.3 48 t127.2 56 t129.4]] It is not known what happens when input differs from the sequence.

#### Alternatives

Assume that two such toy course of events exists. They are described using an **alt**-structure containing the two toy course of events.

| alt[ |                                  |

|------|----------------------------------|

| pa   | ar[                              |

|      | seq[t123.3 56 t127.2 23 t129.4]  |

|      | seq[t123.3 48 t127.2 56 t129.4]] |

| pa   | ar[                              |

|      | seq[t123.3 33 t127.2 24 t129.4]  |

|      | seq[t123.3 48 t127.2 33 t129.4]] |

The unification of the bootstrap distributes the unification to each of the course of events. Assume that the input is the same as in the earlier example (constant). Among the two alternatives the second differ from the input. It is pruned from the alternatives and only the first course of events remains.

#### Any

The last example with two course of events is turned into two behaviors. The first received value 56 is replaced by a predefined behavior **any**. It stands for all possible course of events. It could be considered a wild card.

In this case the input time sequence must have the timing shown. The first value received could be any value. The second value must be either 23 or 24, selecting 56 or 33 as output.

### Symbol

The earlier bootstrap is somewhat changed. The input value should be transported to the output by a symbol. the symbol describes one behavior:

```

def[

par[

seq[t123.3 $ t127.2 any t129.4]

seq[t123.3 48 t127.2 $ t129.4]]

$=any]

```

A **def**-construct is a placeholders for values. The first element is the proper behavior being the result of the construct. The remaining elements are values to be referred. In this case the S=any-behavior. The S= is just a way to tell the reader that this is the S element.

In this case the proper values are the earlier inputoutput behavior modified by a wildcard **any** in the last interval. In the input behavior the first value uses a symbol S. The second value in the output behavior uses the same symbol S.

During execution the input binds S by unification of the input value and **any** resulting in S=input value. Later on the output uses this symbol for output.

If the timing sequence is fulfilled all values from the first input interval is transferred to the output in the second interval.

#### Copies

In the earlier example S was used a some sort of variable. Constants can be used in the same way. The earlier example is modifier with the symbol T:

```

def[

par[

seq[ T S t127.2 any t129.4]

seq[ T 48 t127.2 S t129.4]]

S=any

T= t123.3]

```

The value t123.3 is shared. This is an important feature for representations. Symbols are the only way to specify sharing. Thus all shared structures are in the **def**-structure.

#### Representation

In the earlier example the concept of representation has been ignored. Below a component and three nets are used. The component consists of a **def**'tree structure. The nets by a **par**-list.

```

unify[

par[any 1 2]

apply[

def'[

par[sel'[2] sel'[2] any']

any']]]

```

The **apply**-construct (as a unary operator ) transforms the the representation to its behavior.

The **def**'-structure is a representation. When transformed it becomes a **def**-structure, the 'differs. Its first element is the behavior proper being a **par**structure with two **sel**'-elements and one **any**' element. They are transformed to **sel** and **any** respectively. The **par**-construct is identical in the representation.

Links are not possible to have i the representation. Instead **sel**-elements are used. It selects an addressed element in the surrounding **def**-structure. The address is a tree-index allowing the access of an element far down in a tree structure.

Thus the rewritten example is:

```

unify[

par[any 1 2]

def[

par[S S any]

S=any]]]

```

In some steps it will be rewritten to:

par[1 1 2]

### Function application

Function application is such a general concept that it must have full support. The function application is implemented by the non-unary **apply**-construct.

An example from extended lambda calculus where two numbers 1 and 2 are summed in an embedded expression is:

```

\lambda($1, $2).($1+$2) (1, 2)

```

The same expression is expressed as follows:

Functions have no restrictions on formal arguments as described by the **any**'-elements. Thus a shortcut is performed:

```

def[

apply[+ sel[2] sel[3]]

1

2]

```

The function is transformed from representation. The operator symbol +' has been converted to an instruction. In the **def**-construct the actual arguments are placed after the proper element.

In the next two steps the **sel**-elements selects the actual arguments 1 and 2.

During the next step the function application is performed:

```

def[ 3 1 2]

```

The entire **def**-construct is canonical. The result is the proper element:

### 3

### Logical structure

The execution mechanism could be modeled in an abstract logic model described here. The expressions used in the examples are compound expressions delimited by parenthesis:

unify[5, expr, a]

This structure could not be stored in a memory cell. Instead a number of global symbols, here depicted *identifiers* are used. A definition of the expression for the identifier is placed in each memory cell. It is a function depicted *closure*.

By using the identifiers an arbitrary non circular graph may be constructed. The elements to the left of @ corresponds directly to the elements of the expression above. To the right of @ there is sometimes a reference to a **def**-construct. A number of tags specifies how the closure should be rewritten.

There are some important variants:

$\begin{array}{l} id_2 = unify[5, id_{expr}, \, sel(n_a)] @(env_{defa}, \, tags) \\ id_2 = unify[5, id_{expr}, \, sel(n_a)] @(env_{defa}, \, garb) \\ id_2 = @(free) \end{array}$

The first one is the general one used. The second one is tagged to be tested whether it is garbage. The last one is an unused memory cell.

Execution is by rewriting expressions. They form a number of trees. Any closure may be rewritten. Some would not cause a change. Memory cells are tagged to indicate if to be rewritten, waiting for result and how far to be rewritten. Only pending expressions are rewritten.

In a gross view an expression tree is followed from root to leaves. In some case in a pre-traversal order. Signaling up or down in the tree is performed by rewriting identifiers *id*. Generally, identical identifiers are rewritten in one step.

Garbage collection is performed by rewriting the garb tagged expressions. Those not referred by another expression are turned into **free** cells.

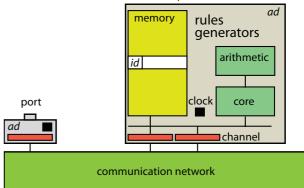

#### Multiprocessor

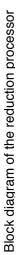

The logic structure is implemented in a multiprocessor. It consists of a communication network, ports and reduction processors. The individual units have a hardware address.

Each reduction processor contains a number of memory cells, one larger cell able to store a two level expression and some network cells.

The core unit contains the larger memory cell. A numeric arithmetic unit is connected to this cell. Within the large memory cell values of single elements could be permuted.

There are some channel units performing communication through the communication network. The channel unit contains one network memory cell. It can store one closure.

Execution is performed either by a network cell or a core cell. All rewriting is performed by inspecting a closure. Therefore a global intra-processor rewrit-

ing is performed by distributing a particular closure to those processors involved.

Rewriting is of two types:

- an *identifier* is rewritten. In parallel all fields in all closures within the local memory is rewritten. By a search mechanism only involved elements are changed.

- a *closure* is rewritten. Depending on the expression one or two levels are used. If two, the other son expressions are read. Rewritings is by permutation of elements and setting tags.

Rewrite rules are implemented in a set of gates. reduction processor

### Time synchronism

Ports time stamp values and control output by time. Clocks in all ports are synchronized to submicrosecond level.

Each separate chip has one phase locked clock. Phase-locking is performed using the communication in the communication network.

### Chip architecture

There was an implementation under design. Experience from that design showed that the main footprint should be altered. This change is shown here. The early design read out a full closure. The new one reads the closure elements in sequence.

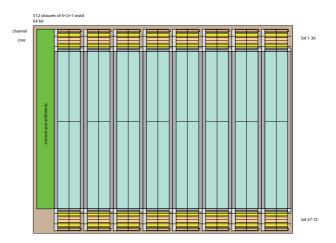

The main part of the chip is memory. The shown memory consists of 8 banks of memory cells. Half of the bits are read/written on one edge, the remaining on the opposite edge. The memory is associative and uses the element as search key.

The core unit and the channel units are place along the other side.

# THE H LANGUAGE

The language of the rp8601 is "**H**". There are several H languages, all being the same but expressed differently:

- the *H<sub>machine</sub>* language consists of a number of lists and scalars. Lists are interconnected by links. Scalars can only be found within lists.

- the *H*<sub>abs</sub> is language corresponding to *H*<sub>machine</sub> where linked expressions are placed inline. *H*<sub>abs</sub> may also be just a scalar. Sharing an expression is expressed by a local symbol referring a definition. This is only a syntactic way to express links. The definition of the shared object is (any order may be used and scope is not defined):

- exp : symbol

There are sugared variants. They are not discussed here. The  $H_{abs}$  is used here because it is the only language that can be written in text.

The H language has a mapping onto real world properties or traits. When written as a syntactic concept it has just an existence, but when executed in a machine the relation to the real world is used. Some of the mechanism can only be understood with the knowledge of a machine. They are not discussed in this section but in subsequent sections. Essentially these mechanisms are not unique for rp8601, but are general concepts of all computing paradigms.

The H language is an applicative language. It has a semantics enabling the control of almost all what is necessary in administrating a system - without having side effects!

The H language is both data and program - all with the same syntax. There is no difference between data and program. Thus there is only one syntactic form.

The H language semantics is not defined by the methods used for classic, functional or other languages. The syntactic form is all. Other languages has some side-effects both in their semantics and syntax. The semantics is here expressed by equivalence rules. They take one syntactic form and describes it to be equivalent to another form. The syntactic form is here depicted <u>expression</u>.

A <u>reduction</u> is the property of a machine using the H language. It assumes a direction of the equivalence. The machine performs graph reduction by replacing an expression by another expression. In the <u>equivalence rules</u> presented further down the left expression is rewritten to the right expression.

### H syntax

Below the complete syntax of Habs is shown. There are token, scalar and list forms.

A token is shown as one bold text.

A scalar is shown as a text scalar(v) with parenthesis containing an argument v. It stands for a numeric value where n indicates an integer and r a real value.

A list is shown as a text **list**[...] followed by a list. If the list is specified " $e_1 \dots e_n$ " it could have any number of elements. " $e_1 e_2 \dots e_n$ " has at least one element. Otherwise it stands for a fixed number specified by the symbols.

```

delta

epsilon

token

token = some', something', empty',

nothing', any'

int (n)

cyc (n)

real (r)

cycfix (r)

symb[n]

phys[n]

type [ e<sub>1</sub> ... e<sub>n</sub> ]

type = par, seq, symb', phys', part', bag',

alt', pri', if', unify', def', sel', apply',

repr', red', alloc', net', time'

part[ e1 ... en ]

some

something

empty

bag[ e<sub>1</sub> ... e<sub>n</sub> ]<sup>1</sup>

alt[ e<sub>1</sub> ... e<sub>n</sub> ]

pri[ e<sub>1</sub> ... e<sub>n</sub> ]

if[ e<sub>1</sub> ... e<sub>n</sub> ]

unify[ e<sub>1</sub> ... e<sub>n</sub> ]

nothing

any

def[ e e<sub>1</sub> ... e<sub>n</sub> ]

sel[ i<sub>1</sub> i<sub>2</sub> ... i<sub>n</sub> ]

sel[ e i<sub>1</sub> i<sub>2</sub> ... i<sub>n</sub> ]

```

<sup>&</sup>lt;sup>1</sup> the bag construct was not a used in the project

```

apply[e_1]

apply[e_1 e_2 \dots e_n]

repr[e_1]

red[e_1 e_2 \dots e_n]

error

alloc[e ad t_f t_t]

alloc[e ad t_f]

alloc[e ad]

alloc[e]

net[id ad]

time[T, accnom, accach]

```

The  $H_{machine}$  language have additional syntactic constructs. They are the general ones recoded and packed into a single scalar:

sel[ i1 i2 ... in ]

phys[ e1 ]

ID[ e1 ]

-- the Habs link

The list variants also have a tag that represents the state of reduction. It will not be defined here. There are two for a user very important ones - **breadth** and **depth** used in scheduling.

### **Numerics**

In conventional computers there was first integer and then floating point. Computer languages have been influenced by this and implement these two numeric types. However working with real-time, physical space and sets there is more to be asked for. Thus the H-language has more numeric types.

Integer and reals are used and implemented as in conventional computers.

#### Cyclic numbers

Some real world properties are cyclic as angles. Another is infinite spaces. Time is a good example. Time could be viewed as being a number in the range minus to plus infinity and having infinite precision. When time is 23:59 on the day and you add 2 minutes it is 00:01 in a cyclic number system with the length of 24:00.

Assume that there is an infinite range of N. A new number Ncyc is defined as:

$N_{cyc} = N \mod I_{cyc}$

used to depict a value in *N*. The representation is ambiguous, there are infinite amount of values in N corresponding to  $N_{cyc}$ . However when using this representation the user "knows" which one being proper. There are operations on this cyclic type:

difference gives a normal number. Cyclic plus or minus a normal number gives a cyclic. Comparing two cyclic is possible if difference is less than *l<sub>cyc</sub>/2*. A cyclic integer is obvious. Compared to a conventional integer it is overflow and the most significant bit that must be handled different. Compares must handle the first bit different.

A cyclic real must be considered different from floating point. The exponent should be considered fixed. Thus the real corresponds to an integer with the scale  $2^{exp}$ . Difference is performed by alignment to the smallest exponent and with normalization. In the add-operation alignment is to the cyclic number (not to the one with largest exponent as in floating point) and there is no normalization.

The length of the cycle  $l_{cyc}$  could be handle in powers of 2. It is possible to go from one cyclic space to another. Therefore the exponent may be changed arbitrarily together with a corresponding shift with  $2^{-\Delta exp}$  of the mantissa. When increasing the exponent an "earlier" value with the new exponent is used as normal. Its least significant bits are set in the mantissa. The application "knows" that the operation is correct.

#### Built-in ranges

The machine performs operations on sets when rewriting unify numerics. Range operations are common in pattern matching. Therefore the numerics are appearing in three sets

| ≤ n: | n |

|------|---|

| = n: | n |

| ≥ n: | n |

The middle one is the common numeric one. The other two are sets. The result of a unification is obvious except for the one defining a range, however being canonical.

### Lists

There are typed lists. The use of different lists is an implementation necessary to separate constructors in the application domain from  $H_{abs}$  syntactic elements. The general list structure has type **par**. **seq** is part of the process concept and is used to differ it from par.

The list consists either of the elements specified, or by a **part** construct. The latter could be considered an open list representing zero or more elements. The part construct partitions a typed list into a hierarchical set of partitions:

```

par[

e1

part[

e2

part[e3 e4]

part[e5]]

part[]

e6]

```

The construct is needed to implement lists. A part containing no elements is equivalent with the token **empty**. The token **empty** in a list could be dropped. A coloured empty token **point** to be used in array arithmetic with infinite spaces has also been considered.

Parts of lists may be shared.

The part construct also facilitates implementation of generators altering the amount of elements in lists, especially where large or unknown amount of elements are used. Tail recursion is eliminated.

### **Bags and alternatives**

Mathematical theory have sets and bags. Elements in sets are unique. Elements in bags may be identical. The rp8601 bag construct is something between: it contains elements and it is not known whether they are unique. Identical elements placed in the bag is not guaranteed to be separated. It is the use of the bag construct that defines whether it is a true mathematical bag or not.

The bag construct is particularly used when pruning alternatives in unification. In this case the mathematical bag semantics is not guaranteed.

Bags are built analogous to lists. Element order in a bag has no meaning. Corresponding to **part** the **alt** construct is used. **nothing** stands for an alt construct being empty. In a bag or alt construct the nothing token can be dropped.

**bag**-constructs may be shared, but not **alt** constructs.

In many constructs the **alt** and **pri** construct may be expanded outside the construct e g:

par[ e1 alt[ e2 e3 ] e4]

is equivalent to

```

alt[

par[ e1 e2 e4 ]

par[ e1 e3 e4 ]

```

# Condition

Conditions are special cases to handle alternatives. The **pri** construct orders alternatives. The construct contains an ordered list of alternatives. The construct equals the first one not being nothing.

The **if** construct is a list of expressions. It could be considered a guarded expression. If some expression is **nothing** the construct equals **nothing** otherwise the first expression.

The combination of pri and if constructs forms a conditional expression:

```

pri[

if[ e<sub>1</sub> c<sub>11</sub> ... ]

```

if[ e<sub>2</sub> c<sub>21</sub> ... ] ... if[ e<sub>n</sub> c<sub>n1</sub> ... ]]

# Sharing and constraints

Graphs are directed constructs. Graphs are formed by constructing (= referencing, see below) using already defined graphs  $e_2 \dots e_n$ . No loops are possible. Lists form an hierarchical construct. They don't allow sharing.

Constraints are conditions defining when an expression is valid. The **def**-construct is used to implement sharing and constraints:

**def**[ e<sub>1</sub> e<sub>2</sub> ... e<sub>n</sub> ]

is considered to be a typed list with special properties. If the typed list exists, it is the equivalent to  $e_1$ . The typed list is said to be the <u>environment</u> to all sub-expressions of the typed list. When referenced all elements  $e_1 e_2 \dots e_n$  are present.

The **sel** construct selects another sub-expression using indexes  $i_1 i_2 \dots i_n$ , each being an integer, using the environment *env*:

sel[ i1 i2 ... in ] @env

which is equivalent to

**sel**[ env i<sub>1</sub> i<sub>2</sub> ... i<sub>n</sub> ]

The first index should be greater than 1 in order not to refer to the first expression. The current understanding here is not clear.

# Representation

In classic programming there are data and program. In H they are the same. However the mode of an expression is either the text or the mathematical interpretation. In some applicative languages there is a Quote function. It is related to representation.

In H there are two forms: the <u>representation</u> and <u>expression</u> forms. Both are expressions. A representation form may be the result of an expression. An expression form is the result of an **appl** (-ication) construct:

apply[e1]

is recursively applied to all subexpressions of  $e_1$ . Any subexpression not yet evaluated is evaluated before the application.

Almost all syntactic elements have equivalence rules used in reductions. In order not to perform such a reduction, an element has a dual correspondence. Thus **unify** has the representation form **unify**'. The corresponding holds for their simplified forms as **any** and **any**'. The simplest scalars and typed lists do not have dual forms. They are the same in both forms.

High order forms of representation is protected by a **repr** construct. An application of such a construct returns the protected expression. By cascading **repr** constructs, any high order mechanism may be constructed.

The high order forms allow high order forms to be "compiled" by a compilation function. This type of functionality could not be expressed in normal applicative languages. High order functions are currently not available in logic languages or process algebras. This is due to the currently used high order function mechanism. The representation in H is a more general mechanism.

The "<u>functional application</u>" is a special form of the application using several expressions. The first expression  $e_1$  is of representation form and the other expressions are actual arguments as shown earlier:

```

apply[ e<sub>1</sub> e<sub>2</sub> ... e<sub>n</sub> ]

```

is equivalent to

```

def[

apply[ e1 ]

e2

...

en]

```

It is very simple to rewrite. The **apply**[e1] creates an instance of e<sub>1</sub>. Subsequently necessary **sel** constructs access the *environment* in which the actual arguments are present.

# **Special generators**

All canonical expressions are an **alt** construct of expressions. It contains all expressions of the H language. When counting expressions it counts to 1. The token **any** stands for any such expression.

One of those expressions is **something**. The contents is hidden. **some** (plural) stands for a **part** construct with at least one **something**.

# Unification

Unification is an arithmetic operation. In other languages it is generally a binding of a symbol to an expressions. The definition of H is in the other direction, it expresses a vast number of alternative expressions where only some are possible. Those possible have proper values for the symbols. The unification evaluates an equality construct, either it results in a proper expression or it prunes the alternative in charge.

An implementation of the symbol arithmetic uses the unification to bind symbols! The complexity comes there. Unification is simple. If several expressions included are identical, the result is such an expression otherwise **nothing**.

### Error

In computing there may be hardware errors. In order to cope with this the machine language, not  $H_{abs}$ , has an additional equivalence rule:

$e_1 = e_2$

That is: any expression  $e_1$  is equivalent to any expression  $e_2$ . Hence the machine is assumed to perform random reduction. To this is added: with low frequency. This is definitively not applicative computing. This is the way hardware errors work.

**error** is a scalar token and **red** (-undancy) is a construct being an ordered list of expressions. The overall view of its use is that **error** propagates upwards in expressions reaching eventually a **red** construct where it is stopped. It is removed from the red construct. The red construct is equivalent to its first expression. Several red constructs may be included in an expression at various places.

Beware of the use of this mechanism. It is dangerous, however probably one of the few ways to cope with errors. Its use could be visualized:

An expression contains subexpressions randomly altering to new ones. The "new" expressions are from user point acceptable but may be different.

A good example of its use: two expressions *a* and *b* in a **red** construct are stored in different physical memories and sharing the same expression *e*<sub>*r*</sub>. An alloc construct, see further down, places an expression in a physical location:

# Symbols and machine symbols

Symbols are different from symbols in other computer languages. They should not be mixed-up.

Assume there are some unique properties. Some could be expressed as data structures others are real world traits. Examples are "that car", "the character L" etc. In the real world they just exist. In understanding the property there may be some description *exps* or none!

The H language has a representation form being:

symb'[ exps ]

The *exps* expression may be empty. There is a corresponding expression form:

### symb[]

It is used in the following way: Some representation form (e g a program) has an internal expression being **symb**'. Performing apply on this structure creates a **symb** construct. Its only purpose is to be a <u>placeholder</u> for something not known. Using the the same **symb**'[*exps*] constructs at different position creates *different* placeholders, hence they are considered different when comparing.

A created **symb** construct could be referenced from several expressions. They can also be compared.

### Physical address

There is a special case of symbols, the machine symbols, here denoted **phys**. These symbols map onto hardware items of the actual physical machine. The difference with a symbol is that the *exps* of the phys is known by the machine. Such symbols are used for "instruction code", "port address" etc.

The semantical understanding is: when building the hardware the symbol was created. The symbol is carried by the phys construct to the machine.

### Internal symbols

The H language does not have symbols. Instead it uses **sel** constructs to select particular expressions from an environment. This selection mechanism is equivalent to an internal symbol.

Some expressions of an environment are the token **any**. At this point it acts as a generator for an arbitrary H expression.

#### Semantics

A graph in a machine defines an expression P. Let each symbol be assigned an expression. The equivalence rules expands this expression to PE. In some cases PE may be empty. Now let each symbol have all arbitrary expressions of H. The cross products of these expressions generates a set PES. Most symbol expression combinations do not generate expressions. The remaining expressions of PES define the expressions in a symbol combination.

#### Symbol arithmetic

In functional applications symbols are placeholders bound to an expression. In logic applications there are a relation between symbols. These relations causes constraints on symbols. Arithmetic on symbols is to solve these constraints.

**isym** used below is included for the explanation, but is not part of the H language.

The graph consists of an arbitrary directed graph. It uses an arbitrary amount of **def** constructs to specify shared data structures, each being an **isym** construct. They are referred to by **sel** constructs. The references could be part of **unify** constructs.

Together the **isym**, **sel** and **unify** constructs form an equation system to solve. The solution may result in several alternative graphs. Thus the symbols are constrained. The complexity of the solving mechanism could be drafted in the levels:

- 1. all referred sharing points are bound to canonical expressions. This is the functional case. There is no additional symbol arithmetic.

- 2. at each sharing point there is at most a canonical expression bound to a symbol. This case corresponds to "equalities between several symbols" assigned to one expression.

- 3. as 2 but there are several unifications containing a symbol and canonical expressions. The unifications can always be reduced to a canonical expression.

- 4. as 3 but there are a set of alternative solutions each needing separate reductions.

- 5. other

The H language could express all four. The machine must have more built in rules when using more complex solutions. The current approach is to solve the first 2 complexities.

### A sketch of arithmetic type 2

An isym construct can have these forms:

- 1. isym[]

- 2. isym[e<sub>can</sub>]

- 3. isym[ e<sub>can,1</sub> ... e<sub>can,N</sub> ]

- 4. isym[ s<sub>2</sub> ]

- 5. **isym**[ s<sub>2</sub> e<sub>can</sub>]

- 6. **isym**[ e(s<sub>2</sub>)]

In the first (1.) variant the symbol is not bound. If this is the final solution it is equivalent to **any**. In the second example the symbol is bound to the expression  $e_{can}$  being canonical. The third variant can be further reduced. The **isym** construct is here equivalent to a **unify** construct. If it rewrites to **nothing** the isym expression equals nothing and it is further propagated in the graph.

The fourth (4.) case contains a reference to another symbol. It states that the current symbol is equivalent to  $s_1$ . The situation is as follows:

s<sub>1</sub>: **isym**[s<sub>2</sub>] s<sub>2</sub>: **isym**[e]

Two symbols are identical. In this case one of them should refer to the other. Using several symbols

referring to each other may cause loops. Symbols are ordered in H. Symbols may refer to symbols before. If  $s_2 < s_1$  the referred order is correct. If  $s_2 = s_1$  the  $s_2$  should be dropped. Otherwise referencing should be swapped:

s<sub>1</sub>: **isym**[] s<sub>2</sub>: **isym**[s<sub>1</sub>e]

The fifth (5.) case is the same as above. If  $s_2 < s_1$  the symbols should be swapped as above. Otherwise the expression *e* should be moved:

```

s<sub>1</sub>: isym[ e ]

s<sub>2</sub>: isym[ s<sub>1</sub> ]

```

The sixth (6.) example contains an expression with a subexpression being a symbol  $s_2$ . In order not to form a loop it must refer to a symbol before. It does not involve additional symbol arithmetic.

### A sketch of arithmetic type 3

Assume that there is a definition containing one symbol involved in a unification:

```

s<sub>1</sub>: isym[ e<sub>1</sub> ]

unify[ s<sub>1</sub> e<sub>2</sub> ]

```

All such constructs are lifted from the expressions into the symbols. The remaining part may have other constructs causing the binding of a symbol (not shown):

s<sub>1</sub>: **isym**[ e<sub>1</sub> **unify**[ e<sub>2</sub> ]] S<sub>1</sub>

There are the following symbols being constrained by the expressions  $e_1$  and  $e_2$ :

```

\begin{array}{ll} s_1: & \mbox{isym}[\ e_1 \ ] \\ s_2: & \mbox{isym}[\ s_1 \ e_2 \ ] \end{array}

```

In the same way as above the constrain expression should be moved towards symbols before. It would result in:

```

s<sub>1</sub>: isym[e<sub>1</sub> e<sub>2</sub>]

s<sub>2</sub>: isym[s<sub>1</sub>]

```

The first symbol could be further reduced as in case 3 above.

#### A sketch of arithmetic type 4

Assume that somewhere in a **def** construct there is a **pri** construct. It contains alternative expressions each referring to the symbol:

```

def[

pri[

e1(S1)

e2(S1)]

S1: isym[]]

```

Each of these alternatives may have constraints. They may differ. To solve this, the **pri** construct is moved outside the **def** construct: pri[

| def[ | e1(s1)                                                              |

|------|---------------------------------------------------------------------|

| def[ | s <sub>1</sub> : <b>isym[]]</b><br>e <sub>1</sub> (s <sub>2</sub> ) |

|      | s <sub>2</sub> : <b>isym[]]]</b>                                    |

This creates two parallel symbol equation systems. Their solutions are separated. In this case symbol  $s_1$  is first evaluated. If  $e_1$  does not produces a result  $s_2$  has to be solved.

### Arithmetic of type 5

Some arithmetic could not be solved except using a special algorithm, e g solving for a trigonometric result equalling its argument:

s<sub>1</sub>: isym[] unify[ s<sub>1</sub> apply[ cos s<sub>1</sub>]]

### H equivalence rules

A <u>root expression</u> is an expression being a top of a graph of expression. A machine may contain any number of root expression. Zero expressions results in an idling machine. Many expression results in separate executions. In this section one root expression is concerned.

### Wellformed

Assume that there is one root expression. It contains generators modeling a "large" graph, in some cases infinite. This graph is rewritten to another graph.

The H language could be reduce to ZERO expressions in some cases. In order to execute there is a main reduction direction to create an existing root expression. Such an expression does only exist if it is not reduced to **error** or **nothing**. The concept of wellformed is introduced:

- An expression is *soft error free* if no expression could create an error from **error**' that propagates to the root. There are simple means by introducing **red** constructs that will guarantee this.

- An expression is *nothing free* if no expression of any type can generate a **nothing** token propagating to the root. There are simple means by introducing **pri** constructs that will guarantee this.

From this follows that all expressions introduced into the by time expanding root graph must be well-formed.

Because the concept of representation is used, any type of user application may result in an expression of representation form. In some cases it is from an input through a port or in other cases from a pseudorandom generator. Hence it is clear that future such expressions are not known.

For proper graph reduction the machine should know this before executing. This is of course impossible. Even if the machine during the start tries to expand the root graph as much as possible it would be impossible to find out the wellformedness.

To lighten the burden of wellformedness the wellformedness should apply to each <u>time step</u> of port behavior and with <u>applicable input data</u>. In such cases the machine would perform graph reductions for the root graph creating one additional output.

During one such step it may be the case that wellformedness is not guaranteed and the root graph is reduced to zero expressions. From H language point of view the already produced output is a failure. No execution should have occurred. The machine and user have made an error that the machine cannot foresee.

Here it assumed that such false output may be the case and is forgiven!

#### Driving

With driving means the mechanism initiating each graph reduction.

The root graph is rewritten in order to find expressions to be **nothing** free. **nothing** may be introduced by an expression of representation form, an empty **alt** construct or a **unify** construct. An expression tree must be scanned for this. Unifications must be performed.

The need for a particular subexpression causes the <u>lazy evaluation</u> mechanism to traverse down an expression to the particular subexpression.

#### Reduction rules

In a separate table the reduction rules are sketched. They are defined by equality. The left expression is reduced to the right expression. There are also restrictions on each expression defining the order the rewrite rules shall be used. They are not shown.

### PROCESS CONCEPT

In this section there is an orientation about applicative processes. In rp8601 the concept is named <u>behavior</u>.

Assume there are a number of resources  $r_n$ , time periods  $T_n$  and expressions  $e_n$ :

$c_n = [e_n r_n T_n]$  $C = \{... c_n ...\}$

A course of events  $c_n$  is the triplet of these. A complete course of events C is a set of such course of

events. T is absolute time period from  $t_b$  to  $t_e$ . The resource  $r_n$  is to house the course of events. It could be a virtual one like speed of subject or the voltage on a physical port. The expression  $e_n$  characterizes the course of events.

The course of events above is a <u>continuous</u> course of events. If the time period is changed to just an event at time  $T_n$  it is a <u>discrete</u> course of events.

A <u>real</u> course of events is what is actual happening in the physical world. The course of events could not be seen. It just exists. A <u>modeled</u> course of events is what is described above, or just short <u>course of events</u>.

Modeled course of events may be included in time sequences where course of events are time slices. Each such course of events could be modeled relative its beginning. Such a time slice is a <u>relative</u> course of events in contrast to an <u>absolute</u>. Instead of a time period it has a <u>duration</u>. The discrete one has a <u>pulse</u>.

#### Model

Current real-time systems cannot model course of events. Instead there is an interaction between the real behavior outside the system and the internal system. Animation software describes modeled course of events. It could be played. A modeled course of events in the rp8601 is implemented with a data structure. It may be analyzed, simulated or played.

#### Behaviors

There are a number of course of events  $C_n$  included in a <u>behavior</u> B:

$B = \{..., C_n ...\}$

Such a set could be the complete set of course of events for a particular item. It could be real word item, a real-time system or some internal process in a computer system. Examples of course of events and behavior expressed in the H language are:

```

C: seq[ Ca Cb Cc Cd Ce Cf ]

B: alt[

seq[ Ca Cb Cc Cd Ce Cf ]

seq[ Ca Cb Cg Ch Ci ]

seq[ Cj Ck Cl Cm ]]

```

A real-time system uses a program that can produce the behavior *B*. After the system has executed it exhibit *C*. The real time system runs and at a particular time, an <u>occasion</u>, it exhibits a <u>state</u>. At the beginning of execution the real-time system has the state *B*, at the end of execution state *C*. At an occasion *b* the state *S*:

```

S: seq[ Ca Cb

alt[

```

```

ConElem = {delta, epsilon, some', something', empty', nothing', any', int(n), cyc(n), real(r), cycfix(r),

some, something}

ConH = {symb', phys', part', bag', alt', pri', if', unify', def', sel', apply', repr', red', alloc', net', time'}

ConList = {par, seq} ∪ ConH

RedElem = {nothing, any}

RedList = {part, if, unify, def, sel, apply, repr, alloc, net, time}

OPS = phys'[...] being built-in operations

INS = symb[ n ] being built-in instructions

type [e_1 \dots part[e_x \dots e_v] \dots e_n] = type [e_1 \dots e_x \dots e_v \dots e_n]

type∈ConList

part[] = empty

type [e_1 \dots e_n] = type [e_1 \dots e_n]

type∈ConList

bag [e_1 \dots alt[e_x \dots e_y] \dots e_n] = bag [e_1 \dots e_x \dots e_y \dots e_n]

type [e_1 ... nothing ... e_n] = type <math>[e_1 ... ... e_n]

type∈{bag, alt, pri}

type [e_1 \dots nothing \dots e_n] = nothing

type∈ConList ∪ RedList

type [] = nothing

type∈{alt, pri, if}

type [e_1] = e_1

type { alt, pri, if, unify }

type [e_1 \dots e_x \dots e_y \dots e_n] = type [e_1 \dots e_y \dots e_x \dots e_n]

type { bag, alt, unify }

type∈{if, def}, x>1, y>1

type [e_1 e_2 ... e_x ... e_y ... e_n] = type [e_1 ... e_y ... e_x ... e_n]

type[e_1 \dots type[e_x \dots e_y] \dots e_n] = type[e_1 \dots e_x \dots e_y \dots e_n]

type∈{alt, pri, if, unify}

type1[e_1 \dots type2[e_x \dots e_y] ... e_n]

type1∈ConList ∪ RedList, type2 = {alt, pri}

= type2[ type1 [ e<sub>1</sub> ... e<sub>x</sub> ... e<sub>n</sub>] ... type1[ e<sub>1</sub> ... e<sub>y</sub> ... e<sub>n</sub>]]

if[e_1 e_2 ... e_n] = e_1

\forall x > 1: notNothing(e_x)

if[e_1 e_2 ... any ... e_n] = if<math>[e_1 e_2 ... e_n]

unify[] = any

unify[e_1 ... any ... e_n] = unify<math>[e_1 ... e_n]

type∈ConElem

unify[ e e ] = e

unify[ symb[ n ] symb[ n ] ] = symb[ n ]

unify[type[a_1 ... a_n] type[b_1 ... b_n]] = type[unify[a_1 b_1] ... unify[a_n b_n]]

unify[ type1[ a_1 ... a_x ] type2[ b_1 ... b_y ] ] = nothing

(x \neq y \cup type1 \neq type2) \cap type \in ConList

def[e_1 \dots e_n] = def[e_1@[e_1 \dots e_n] ... e_n@[e_1 \dots e_n]]

type [e_x ... e_y] @ [e_1 ... e_n]

tvpe≠def

= type [e_x@[e_1 ... e_n] ... e_y@[e_1 ... e_n]]

e@[e_1...e_n] = e

type∈ConElem ∪ {nothing, any, error}

sel[i_1 \dots i_n]@[e_1 \dots e_n] = sel[@[e_1 \dots e_n]i_1 \dots i_n]

sel[ e<sub>1</sub> ] = e<sub>1</sub>

sel[@[e_1 \dots e_x \dots e_n]i_x \dots i_n] = sel[e_x \dots i_n]

sel[ type[ e_1 \dots e_n] i_x \dots i_n] = sel[ e_1 i_x \dots i_n]

type\in{def, red}, \forallx-1: notNothing(e<sub>x</sub>)

apply[repr[e_1]] = e_1

apply[ symb'[ e1 ... en ]] = symb[ uniqueNumber ]

apply[ phys'[ e1 ... en]] = hardwareDependent

apply[ type'[ e<sub>x</sub> ... e<sub>y</sub> ]] = type[ apply[ e<sub>x</sub> ] ... apply[ e<sub>y</sub> ]]]

type'\inConH \cap {symb, phys}

e₁∉INS

apply[e_1 e_2 ... e_n] = def[apply[e_1]e_2 ... e_n]

apply[e1 e2 ... en] = nothing

e_1 \in INS, \exists x > 1: not notNothing(e_x)

red[] = error

red[ e1 ... ] = e1

red[e_1 ... error ... e_n] = red[e_1 ... ... e_n]

```

Equivalence rules for H language. Internal symbols is an implementation issue.

```

part[ c<sub>c</sub> c<sub>d</sub> c<sub>e</sub> c<sub>f</sub> ]

part[ c<sub>g</sub> c<sub>h</sub> c<sub>i</sub> ]]]

```

The course of events  $c_a c_b$  have been passed. They are said to be the <u>history</u>. The remaining part is a behavior described by the alt construct. The real-time system prunes the alternative gradually as time elapses.

The history is generally a very large data structure. Some of this data structure may be forgotten because it is of no use for the application:

```

S: seq[ some cb

alt[

part[ cc cd ce cf ]

part[ cg ch ci ]]]

```

### Generators

Behaviors may be very complex. Most such could not be programmed in any available computer language. Simplified, but good enough, mechanisms may be used. They are discussed.

There are <u>parallel</u> course of events  $s_1$ ,  $s_2$  and  $s_3$ :

```

P:

par[

s1:

seq[ Ca Cb Cc Cd Ce Cf ]

s2

seq[ Ca Cb Cg Ch Ci ]

s3

seq[ Ci Ck Ci Cm ]]

```

They may have different duration. The specification of  $c_x$  defines the time periods.

A <u>grammar</u> may be used to generate a behavior. It should include the basic concept, seq and par structure. The method is versatile when generating waveforms.

In an analogous way <u>state machines</u> may be implemented. State machines are equivalent with grammars. Conversion from one specification to the other is possible. One state in a state machine is described by a generator for that state. The state machine contains a number of generators  $G_n$  and an initial generator *IN*:

```

def [

IN

G<sub>1</sub> ... G<sub>N</sub>]

G<sub>x</sub>: part[ c<sub>x</sub>

alt[ G<sub>y</sub> ... G<sub>z</sub> ]]

```

Grammar and state machine together with the basic method form three different forms to represent a behavior. Conversion between them is possible. All basic behaviors cannot be expressed in a grammar or a state machine.

#### Constructing

Assume that there exists a number of behaviors modeling proper issues. Now use three of them  $b_1$ ,  $b_2$  and  $b_3$ :

```

b<sub>1</sub>: seq[ ... ]

b<sub>1</sub>

local<sub>A</sub>(b<sub>1</sub>, b<sub>2</sub>)

b<sub>2</sub>

b<sub>2</sub>: seq[ ... ]

b<sub>2</sub>

local<sub>B</sub>(b<sub>2</sub>, b<sub>3</sub>)

b<sub>3</sub>: seq[ ... ]

```

Here  $b_1$  and  $b_2$  are duplicated being 2 and 3 separate behaviors. Two groups *A* and *B* are formed. *A* contains  $b_1$  and  $b_2$  and a local expression using them. B contains  $b_2$  and a local behavior  $b_3$  and an expression using them. Group A and B communicate by the  $b_2$  behavior. A and B can both be rewritten as separate modules. In the module concept the local references are implemented as unification with the external behaviors:

```

def[

b<sub>1</sub>: seq[ ... ]

b<sub>2</sub>: seq[ ... ]

unify[ par[ b<sub>1</sub> b<sub>2</sub> ] A ]

unify[ b<sub>2</sub> B ]

A: def[

par[d<sub>1</sub> d<sub>2</sub>]

local<sub>A</sub>(d<sub>1</sub>, d<sub>2</sub>)]

B: def[

C<sub>2</sub>

local<sub>B</sub>(c<sub>2</sub>, b<sub>3</sub>)

b<sub>3</sub>: seq[ ... ]]

```

#### Messages

H does not have message passing. However a parameter transfer can be written in a way rather similar to message passing. In order to describe this there are three behaviors. Earlier it was shown how such three behavior are used to connect two modules. One in each module and one between the modules. Now ignore the modules. View three corresponding elements of the behaviors:

- $b_1: \quad \textbf{seq}[\ \dots\ \textbf{duration}[\ e_n\ ad_n\ T_f\ T_t]\ \dots\ ]$

- $b_2: \quad \textbf{seq}[\ \dots \ \textbf{pulse}[\ e_n \ ad_n \ T_f] \ \textbf{pulse}[\dots \ T_t] \ \dots \ ]$

- b<sub>3</sub>: seq[ ... duration[  $e_n ad_n T_f T_t$ ] ... ]

There is a flow from  $b_1$  to  $b_2$  and  $b_3$ . The specification of the basic course of events has not yet been standardized. There are two constructors *duration* and *pulse*. The first duration is rewritten by some not shown function to a pulse when issued at the beginning of the period  $T_f$ . The next pulse comes at the next duration.  $T_t$  is known there. With the knowledge of two adjacent pulses the duration in  $b_3$ could be evaluated. There is as shown above a method going from duration to pulses. The pulses correspond somewhat to conventional messages.

A behavior uses symbols to transfer expressions. The expressions may be used in functions evaluating new expressions. These new expressions my be needed in real time. In a <u>well-formed real behavior</u> the evaluation is possible in real time. This means that a value to be bound in future cannot be used now!

#### Time and order

An absolute time has been used in course of events of earlier examples. This could be lightened. It is discussed here. For the moment assume there is only pulse course of events and ignore everything except the time T. Use the symbol  $\Delta$  to indicate a pulse.

There are two parallel courses of events

```

par[

```

$\begin{array}{c} \textbf{seq} [ \ T_1 \ \Delta_1 \ T_2 \ \dots \ T_3 \ \Delta_3 \ \dots \ ] \\ \textbf{seq} [ \ T_4 \ \Delta_4 \ T_5 \ \dots \ T_6 \ \Delta_6 \ \dots \ ] \\ \end{array}$

In this example all pulses are placed in time. There is no ambiguity. If  $T_1 = T_2 = T_3$  it is possible to eliminate all by the first  $T_1$ . The same applies to the second behavior.

Now assume all times except  $T_1$  and  $T_4$  are slightly different. There may be a behavior that is not strict (not using) in these times. In this case just the order have importance and the times could be dropped. This could be generalized by using cascaded sequences:

```

\begin{array}{l} \textbf{par[}\\ \textbf{seq[} \ \textbf{T}_1 \ \textbf{seq[} \ \boldsymbol{\Delta}_1 \ \dots \ \boldsymbol{\Delta}_3 \ \textbf{]]}\\ \textbf{seq[} \ \textbf{T}_4 \ \textbf{seq[} \ \boldsymbol{\Delta}_4 \ \dots \ \boldsymbol{\Delta}_6 \ \textbf{]]]} \end{array}

```

With this method it is possible to encapsulate pulses in sequences that are understood by the application. There may be parallel behaviors. They may be rewritten to sequences of parallel behaviors:

```

\begin{array}{c} \textbf{seq[} \quad \textbf{T}_1 \; \textbf{par[} \\ \quad \textbf{seq[} \; \Delta \ldots \; \Delta \;] \\ \quad \textbf{seq[} \; \Delta \ldots \; \Delta \;] \\ \textbf{T}_4 \; \textbf{par[} \\ \quad \textbf{seq[} \; \Delta \ldots \; \Delta \;] \\ \quad \textbf{seq[} \; \Delta \ldots \; \Delta \;] \\ \quad \textbf{seq[} \; \Delta \ldots \; \Delta \;] \\ \end{array}

```

All these changes relies on a wellformed expression understanding the sequences. Each parallel sequence could be considered a single transaction.

There may be expressions having a semantics over unsynchronized behaviors. They have to inspect the time order.

# **EXECUTION MECHANISM**

In this section a "machine" performing the execution of the H-language is described. It is a theoretical machine that has to be refined. It is based on the availability of unlimited resources. Thus word length, number of memory cells etc are of arbitrary size. In subsequent sections this model is refined.

### Graph rewriting

Graf rewriting is based on an application divided into a number of expression. Expressions refer to each other by identifiers.

The execution mechanisms consists of a number of processes each being an expression or an identifier. If an expression or identifier is not fulfilling certain characteristics the process is waiting otherwise it is active. Therefore numerous processes may rewrite in parallel. Therefore *massive parallelism* is available being a potential for highest possible execution speed.

The software engineer expressing his solution in a language may use a "parallel" or "sequential" way. A good example on this difference is parallel versus standard sequential sort algorithms.

Another more *fundamental problem* in applicative languages based on  $\lambda$ -calculus is the use of tail-recursion to construct lists. Tail recursion is a very sequential implementation. Modern functional languages as Mathematica has replaced this by generators!

### Closures